Assaig d'oblies

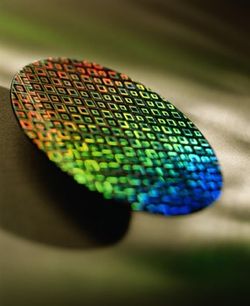

L'assaig d'oblies és un test que es realitza durant la fabricació de dispositius semiconductors un cop finalitzat el procés BEOL. Durant aquest pas, realitzat abans que una oblia s'enviï a la preparació dels daus, tots els circuits integrats individuals que hi ha a l'oblia són provats per detectar defectes funcionals aplicant-hi patrons de prova especials. La prova d'oblies es realitza mitjançant un equip de prova anomenat sonda d'oblies. El procés de prova d'oblies es pot referir de diverses maneres: la prova final d'oblies (WFT), la classificació electrònica de daus (EDS) i la sonda de circuit (CP) són probablement les més habituals.[1]

Un sondador d'oblies és una màquina utilitzada per a la verificació de circuits integrats amb la funcionalitat dissenyada. És un equip de prova manual o automàtic. Per a les proves elèctriques, un conjunt de contactes microscòpics o sondes anomenades targeta de sonda es mantenen al seu lloc mentre l'oblia, muntada al buit en un mandril d'oblies, es mou al contacte elèctric. Quan un dau (o matriu de daus) s'ha provat elèctricament, el sondeig mou l'oblia a la següent dau (o matriu) i la següent prova pot començar. El sondador d'oblies sol ser responsable de carregar i descarregar les oblies del seu suport (o casset) i està equipat amb òptiques de reconeixement de patrons automàtics capaços d'alinear l'oblia amb la suficient precisió per garantir un registre precís entre els coixinets de contacte de l'oblia i les puntes de les sondes.[2]

Per als paquets de múltiples daus actuals, com ara el paquet a escala de xip apilat (SCSP) o el sistema en paquet (SiP), el desenvolupament de sondes sense contacte (RF) per a la identificació de dau provat conegut (KTD) i dau bo conegut (KGD) són fonamentals per augmentar el rendiment global del sistema.

El sondador d'oblies també exerceix qualsevol circuit de prova a les línies de traçat d'oblies. Algunes empreses obtenen la major part de la seva informació sobre el rendiment del dispositiu a partir d'aquestes estructures de proves de línia d'escriptura.[3][4][5]

Quan tots els patrons de prova passen per a un dau específic, la seva posició es recorda per a un ús posterior durant l'encapsulat de CI. De vegades, un dau té recursos de recanvi interns disponibles per a la reparació (és a dir, IC de memòria flaix); si no supera alguns patrons de prova, es poden utilitzar aquests recursos de recanvi. Si no és possible la redundància del dau fallit, el dau es considera defectuós i es descarta. Els circuits que no passen normalment es marquen amb un petit punt de tinta al mig del dau, o la informació de passar/no passar s'emmagatzema en un fitxer, anomenat wafermap. Aquest mapa classifica els encunys de pas i de no pas fent ús de papereres. Aleshores, una paperera es defineix com un dau bo o dolent. A continuació, aquest wafermap s'envia al procés de fixació de daus que després només recull els circuits de pas seleccionant el nombre de safata de daus bons. El procés on no s'utilitza cap punt de tinta per marcar els encunys dolents s'anomena mapatge de substrat. Quan s'utilitzen punts de tinta, els sistemes de visió dels equips de manipulació de daus posteriors poden desqualificar el dau reconeixent el punt de tinta.

Referències

modifica- ↑ «What is a wafer prober? - Technical Column - Technology - MICRONICS JAPAN CO.,LTD.» (en anglès). https://www.mjc.co.jp. Arxivat de l'original el 2022-11-10. [Consulta: 10 novembre 2022].

- ↑ «https://www.waferworld.com/post/importance-testing-silicon-wafers» (en anglès). https://www.waferworld.com.+[Consulta: 10 novembre 2022].

- ↑ "Startup enables IC variability characterization" Arxivat 2016-09-16 a Wayback Machine. by Richard Goering 2006

- ↑ "Testing LCD Source Driver IC with Built-on-Scribe-Line Test Circuitry" (abstract)

- ↑ Design for Manufacturability And Statistical Design: A Constructive Approach, by Michael Orshansky, Sani Nassif, Duane Boning 2007. ISBN 0-387-30928-4 ISBN 978-0-387-30928-6 p. 84